Introdução

Ao longo do tempo os equipamentos têm agregado mais e mais funções, a utilização de circuitos integrados é cada vez mais comum e intensa. A implantação de barramentos de comunicação paralelos está cada vez mais inviável pela complexidade e quantidade das conexões, de forma que a comunicação serial entre os dispositivos se torna uma necessidade bastante presente.

O estabelecimento de linhas de transmissão de dados mais simples em si justifica amplamente a seleção da modalidade serial se comparados os problemas inerentes de linhas de transmissão paralelas, com os inevitáveis problemas de intermodulação entre as muitas linhas de sinal.

As técnicas disponíveis de interligação serial entre dispositivos podem ser classificadas em duas grandes categorias, a comunicação assíncrona e a comunicação síncrona. Estes três métodos têm ocupado posições de destaque:

- Universal Asynchronous Receiver Transmitter – UART;

- Serial Peripheral Interface – SPI; e

- Inter Integrated Circuit – I²C

Há grande familiaridade com a comunicação serial assíncrona por meio do padrão UART (RS-232C). Mas há grandes vantagens na utilização de comunicação serial síncrona ao invés da assíncrona. Além disso, há grandes diferenças entre protocolos síncronos. Apesar de cada protocolo definir limites máximos de taxas de transferência, os diversos fabricantes têm liberdade em desenvolver dispositivos com velocidades próprias. Abaixo uma tabela consolida um comparativo simples entre padrões de dispositivos seriais.

| Tecnologia | Barramento de comunicação | Taxa de transferência máxima | Fluxo de dados |

| UART (RS-232) | 2 | 115kbps | Half ou Full Duplex |

| SPI | 3+n escravos | 2Mpbs | Full Duplex |

| I²C | 2 a 127 dispositivos | 400kpbs | Half Duplex |

Há diversos exemplos no mercado mostrando que estes limites podem ser ultrapassados, por exemplo, memórias SPI que podem chegar a 66Mbps e I²C até 1Mbps.

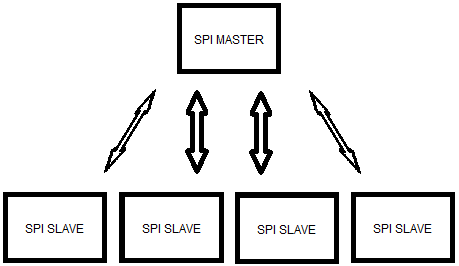

A comunicação síncrona define o conceito de Master/Slave (Mestre – Escravo). Normalmente, o gerador do sinal de sincronismo é o Mestre da comunicação. Os dispositivos que utilizam o sinal de sincronismo são definidos como Escravos. A conexão mais comum desse tipo de comunicação é um Mestre e vários Escravos.

Comunicação SPI

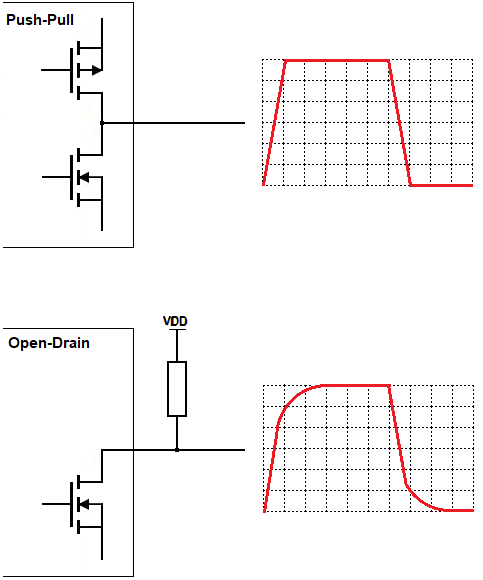

A comunicação SPI tem algumas características basilares. Primeiro os sinais de comunicação têm sentido fixo e definido. Isso implica em sempre haver dois transistores definindo o estado de um pino (estágio de saída Push-Pull). Essa característica é um grande diferencial com outros padrões de comunicação serial como I²C e OneWire, que têm o mesmo barramento de dados para os sinais de entrada saída através do esquema de open-drain (Pull-Up).

Apesar de utilizar duas vias de comunicação ao invés de uma, é possível atingir velocidades maiores, pois há menor deformação do sinal como mostrado na Figura 2 acima.

Outra característica é que toda troca de dados ocorre sempre em ambas as direções. Ou seja, a cada bit enviado do Mestre para o Escravo corresponde um bit no caminho oposto, caracterizando uma comunicação sempre Full Duplex.

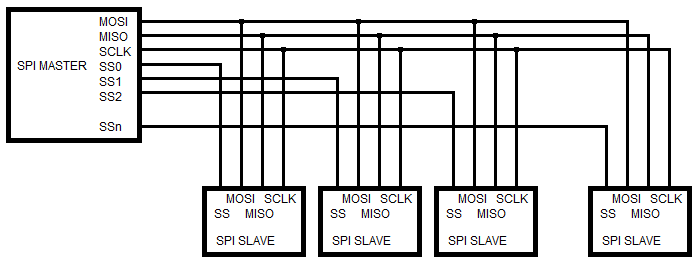

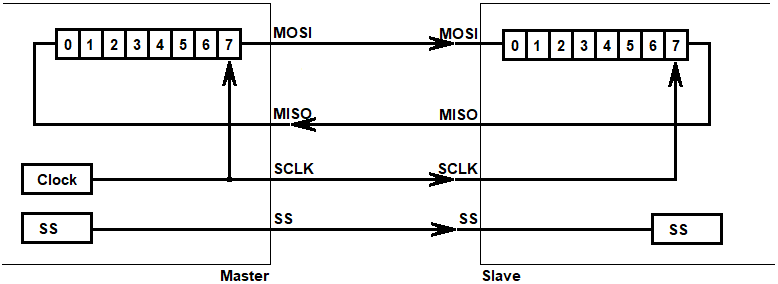

Os pinos básicos de comunicação entre dispositivos SPI e o esquema padrão de conexão para escravos independentes são como abaixo:

| Pino | Nome | Significado | Nomes Alternativos |

| Mestre para Escravo | MOSI | Master Output Slave Input | SDO, DOut, SO |

| Escravo para Mestre | MISO | Master Input Slave Output | SDI, DIn, SI |

| Clock | SCLK | Serial Clock | SCK, CLK |

| Seleção de Escravo | SS | Slave Select | CS, nSS, nCS |

O sinal SS funciona selecionando escravos (um por vez). É um sinal ativo em nível lógico baixo, o que implica em lógica de seleção negativa no escravo. Porém muitos dispositivos utilizam este sinal como sincronismo de quadro (frame). Isto denota a importância de respeitar este sinal.

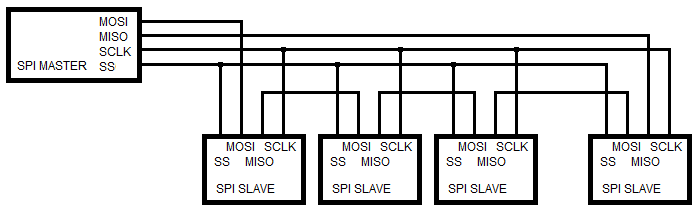

Alternativamente, é possível vincular os escravos efetuam uma conexão Daisy chain, ou encadeada, onde todos os escravos são simultaneamente selecionados e a saída de um escravo é conectada a entrada do próximo. A porta SPI de cada escravo é projetada para enviar durante o segundo grupo de pulsos de clock uma cópia exata de os dados que recebeu durante o primeiro grupo de pulsos de clock. A cadeia com um todo funciona tal qual um único shift-register. O encadeamento em margarida, geralmente, é feito para fornecer um bando de entradas ou saídas por meio de SPI. Cada escravo copia a entrada para a saída no próximo ciclo de clock até que a linha SS ativa baixa seja feita alta. Desta forma apenas uma única linha SS é requerida do mestre, ao invés de uma linha SS exclusiva para cada escravo.

Princípio de funcionamento

O princípio básico de um dispositivo SPI é o registrador de deslocamento (shift-register). Esse dispositivo faz a serialização de um dado paralelo de acordo com o clock. Da forma análoga é capaz de efetuar o oposto, recebendo uma cadeia seriada de bits e convertendo-a em um dado paralelo.

A interface não é apenas capacitada a fazer a conversão serial/paralelo, também conta com o gerador de clock (no elemento mestre) entre 10KHz e 100MHz, o controle para troca do frame e o slave-select. Constituindo assim um dispositivo de comunicação completo. Na Figura 6 abaixo podemos observar como é disposto

Sincronismo do Sinal de Relógio

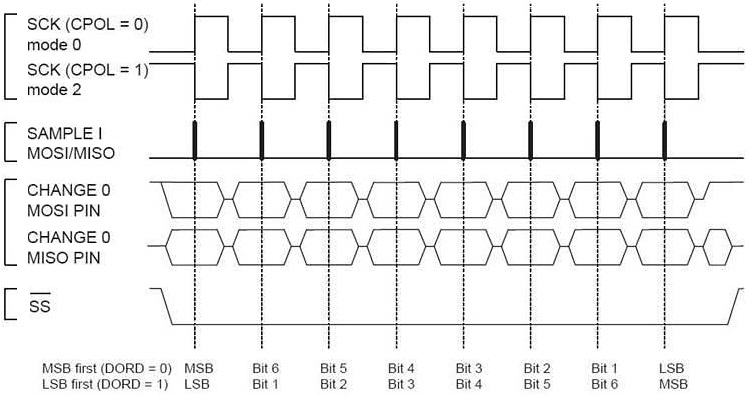

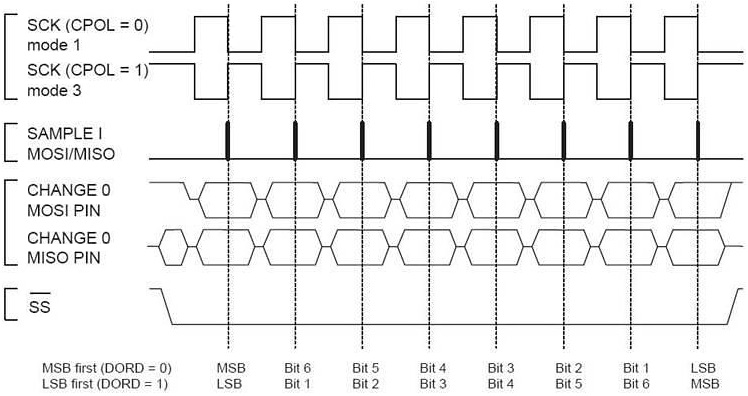

Com a sincronização em mente, a função de Mestre não termina simplesmente com a geração de pulsos de clock em certa frequência. Na verdade, Mestre e Escravo devem operar num protocolo de sincronização em particular, ou os dados serão perdidos. A comunicação SPI é flexível permitindo a configuração de polaridade e de fase do clock. Aqui entram os conceitos de polaridade (CPOL) e de fase CPHA do clock.

CPOL – Polaridade do clock (Clock POLarity) determina o valor base do clock, isto é, o seu valor quando o barramento está ocioso.

- Com CPOL = 0, o valor base do relógio é zero, ou seja, SCLK é “baixo” quando a comunicação está ociosa;

- Com CPOL = 1, o valor base do relógio é um, ou seja, SCLK é “alto” quando a comunicação está ociosa.

CPHA – Fase de clock (Clock PHAse) determina em qual transição do clock os dados serão amostrados (capturados).

- Com CPHA = 0, os dados são amostrados na borda de subida do clock;

- Com CPHA = 1, os dados são amostrados na borda de descida do clock.

Dessa forma os modos possíveis são quatro mostrados na Tabela 3 a seguir:

| Modo | CPOL | CPHA | Borda de troca | Transição | Nível em IDLE |

| 0 | 0 | 0 | Subida | Meio do bit | 1 |

| 1 | 0 | 1 | Descida | Começo do bit | 0 |

| 2 | 1 | 0 | Descida | Meio do bit | 0 |

| 3 | 1 | 1 | Subida | Começo do bit | 1 |

Outra característica fundamental na comunicação é a definição da posição do bit mais significativo (MSB). Através de DORD é possível definir que o bit mais significativo será o primeiro (DORD=0), ou o último (DORD=1) bit transacionado. É possível observar todas essas características através dos dois diagramas de tempo a seguir:

NOTA: Diagramas de tempo obtidos em <http://maxembedded.com/2013/11/serial-peripheral-interface-spi-basics/>

Prós e Contras

Vantagens

- Comunicação full duplex na versão padrão do protocolo;

- Os acionadores push-pull fornecem boa integridade de sinal e alta velocidade, em oposição ao dreno aberto;

- Maior rendimento do que I2C ou SMBus. Não se limita a qualquer velocidade máxima de clock, permitindo potencialmente alta velocidade;

- Flexibilidade total do protocolo para os bits transferidos;

- Não se limita a palavras de 8 bits;

- Escolha arbitrária de tamanho, conteúdo e finalidade da mensagem;

- Interface de hardware extremamente simples;

- Requisitos de energia típicos mais baixos do que no I2C ou SMBus devido a menor quantidade de circuitos (incluindo resistores pull up);

- Sem arbitragem ou modos de falha associados – ao contrário do barramento CAN

- Escravos usam o relógio do mestre e não precisam de osciladores de precisão

- Escravos não precisam de um endereço único – ao contrário do I2C, GPIB ou SCSI;

- Transceptores não são necessários – ao contrário do barramento CAN;

- Usa apenas quatro pinos de circuitos integrados e conecta layouts com menos fios ou conectores. Muito menos que interfaces paralelas;

- Apenas um sinal de barramento exclusivo por dispositivo (chip select) todos os outros são compartilhados;

- Os sinais são unidirecionais, permitindo fácil isolamento galvânico;

- Implementação simples de software.

Desvantagens

- Requer mais pinos de circuitos integrados do que I2C, mesmo na variante de três fios;

- Nenhum endereçamento in-band; sinais de seleção extras ao barramento são necessários para barramentos compartilhados;

- Nenhum controle de fluxo por hardware pelo escravo (mas o mestre pode atrasar a próxima borda do relógio para diminuir a taxa de transferência);

- Nenhum reconhecimento de escravo por hardware (o mestre pode estar transmitindo para lugar nenhum e não sabe);

- Normalmente suporta apenas um dispositivo mestre (depende da implementação de hardware do dispositivo);

- Nenhum protocolo de verificação de erros é definido;

- Sem um padrão formal, validar a conformidade não é possível;

- Lida somente com distâncias curtas em comparação com RS-232, RS-485 ou CAN-bus; (Sua distância pode ser estendida com o uso de transceptores como o RS-422.)

- Opto-isoladores no caminho do sinal limitam a velocidade do clock para a transferência do MISO devido aos atrasos adicionados entre o clock e os dados;

- Muitas variações existentes, dificultando a localização de ferramentas de desenvolvimento, como adaptadores de host que suportem essas variações;

- O SPI não suporta hot swapping (adição dinâmica de nós);

- As interrupções devem ser implementadas com sinais extras ao barramento ou falsificadas usando-se de pollings periódicos de maneira similar ao USB 1.1 e 2.0;

- Algumas variantes, como o SPI duplo, quad SPI e os barramentos seriais de três fios, são half duplex.

Mais sobre assuntos correlatos

- Arquivos Comunicação SPI. Disponível em <https://www.embarcados.com.br/serie/comunicacao-spi/> acessado em 15/jul./2019

- Comunicação SPI – Parte 1. Disponível em <https://www.embarcados.com.br/spi-parte-1/> acessado em 15/jul./2019

- Comunicação SPI – Parte 2. Disponível em <https://www.embarcados.com.br/comunicacao-spi-parte-2/> acessado em 15/jul./2019

- Serial Peripheral Interface – SPI Basics. Disponível em <http://maxembedded.com/2013/11/serial-peripheral-interface-spi-basics/> acessado em 15/jul./2019

- Wikipédia. Serial Peripheral Interface. Disponível em <https://en.wikipedia.org/wiki/Serial_Peripheral_Interface> acessado em 15/jul./2019

- Comunicação SPI – Parte 3 – Microcontrolador AT89S8253 + EEPROM 25LC256. Disponível em <https://www.embarcados.com.br/comunicacao-spi-parte-3-at89s8253/> acessado em 15/jul./2019

- Mundo Projetado. Comunicação Serial Assíncrona. Disponível em <http://mundoprojetado.com.br/comunicacao-serial-assincrona/> acessado em 15/jul./2019

- Mundo Projetado. SPI. Disponível em <http://mundoprojetado.com.br/spi/> acessado em 15/jul./2019

- Mundo Projetado. I²C. Disponível em <http://mundoprojetado.com.br/i2c/> acessado em 15/jul./2019

- Mundo Projetado. RS-485. Disponível em <http://mundoprojetado.com.br/rs-485/> acessado em 15/jul./2019

- Mundo Projetado. Modbus RTU – O que é e como funciona. Disponível em <http://mundoprojetado.com.br/modbus-rtu-o-que-e-e-como-funciona/> acessado em 15/jul./2019

- Mundo Projetado. Implementando Modbus RTU no Arduino. Disponível em <http://mundoprojetado.com.br/implementando-modbus-rtu-no-arduino/> acessado em 15/jul./2019

- Hélio Sousa Mendonça. Disponível em <https://paginas.fe.up.pt/~hsm/docencia/comp/uart/> acessado em 15/jul./2019

- Hélio Sousa Mendonça. SPI e I2C. Disponível em <https://paginas.fe.up.pt/~hsm/docencia/comp/spi-e-i2c/> acessado em 15/jul./2019

- MC68HC11A8 Techinical Data – Serial Peripheral Interface. Disponível em <http://ee.hawaii.edu/~tep/EE491E/Notes/HC11A8/HC11A8_SPI.pdf> acessado em 15/jul./2019

- Texas Instruments. KeyStone Architecture Serial Peripheral Interface. Disponível em <http://www.ti.com/lit/ug/sprugp2a/sprugp2a.pdf> acessado em 15/jul./2019

Referências

Embarcados. Arquivos Comunicação SPI. Disponível em <https://www.embarcados.com.br/serie/comunicacao-spi/> acessado em 15/jul./2019

Embarcados. Comunicação SPI – Parte 1. Disponível em <https://www.embarcados.com.br/spi-parte-1/> acessado em 15/jul./2019

Embarcados. Comunicação SPI – Parte 2. Disponível em <https://www.embarcados.com.br/comunicacao-spi-parte-2/> acessado em 15/jul./2019

maxEmbedded. Serial Peripheral Interface – SPI Basics. Disponível em <http://maxembedded.com/2013/11/serial-peripheral-interface-spi-basics/> acessado em 15/jul./2019

Wikipédia. Serial Peripheral Interface. Disponível em <https://en.wikipedia.org/wiki/Serial_Peripheral_Interface> acessado em 15/jul./2019

Excelente artigo vem bem de encontro com um projeto que estou desenvolvendo que consiste em biblioteca para o Arduino e shift-registers. Parabéns pela pesquisa

Obrigado Sérgio, seu elogio é um grande incentivo e faz valer a pena o trabalho que dá fazer estes artigos.

A produção é um pouco lenta, mas o que quero é não parar com a iniciativa de forma alguma.

Forte abraço e a gente vai se trombando pelos aís do caminho